# 一种有限脉冲响应滤波器

申请号:201110442668.8 申请日:2011-12-27

申请(专利权)人 中国科学院自动化研究所

地址 100190 北京市海淀区中关村东路95号

发明(设计)人 王东琳 尹磊祖 谢少林 汪涛 张志伟

主分类号 H03H17/02(2006.01)I

分类号 H03H17/02(2006.01)I

公开(公告)号 102510273A

公开(公告)日 2012-06-20

专利代理机构 中科专利商标代理有限责任公司 11021

代理人 周国城

www.soopat.com

注:本页蓝色字体部分可点击查询相关专利

### (19) 中华人民共和国国家知识产权局

# (12) 发明专利申请

(10)申请公布号 CN 102510273 A (43)申请公布日 2012.06.20

- (21)申请号 201110442668.8

- (22)申请日 2011.12.27

- (71) 申请人 中国科学院自动化研究所 地址 100190 北京市海淀区中关村东路 95 号

- (72) **发明人** 王东琳 尹磊祖 谢少林 汪涛 张志伟

- (74) 专利代理机构 中科专利商标代理有限责任 公司 11021

代理人 周国城

(51) Int. CI.

*H03H 17/02* (2006. 01)

权利要求书 3 页 说明书 12 页 附图 9 页

#### (54) 发明名称

一种有限脉冲响应滤波器

#### (57) 摘要

本发明公开了一种有限脉冲响应 FIR 滤波器。该FIR滤波器由滤波系数缓冲器、待滤波数据缓冲器、乘法器、累加器、累加寄存器和比较器构成。其中滤波系数缓冲器用来缓冲滤波器中用到的系数,待滤波数据缓冲器用来缓冲待滤波数据,乘法器用来计算单个滤波系数与 BS 个待滤波数据的乘法结果,累加器用来计算乘法器输出和累加寄存器输出的和,累加寄存器用来存放累加器的结果,比较器的输出用来指示当前累加器的输出是否为滤波输出。本发明 FIR 滤波器可以达到并行计算的高效率。

1. 一种有限脉冲响应 FIR 滤波器, 其特征在于, 包括:

滤波系数提供模块,用于预存K个滤波系数;在第n个运算周期,接收到读使能信号后,提供1个滤波系数H(i);

待滤波数据提供模块,用于预存  $N_x$  个待滤波数据;在第 n 个运算周期,接收到读使能信号后,提供 1 个待滤波数据组,该待滤波数据组包括 BS 个待滤波数据:X(nBS-i),X(nBS-i+1), ……,X[(n+1)BS-i-1],当待滤波数据的向量索引小于 0 时,该待滤波数据以 0 代替:

乘法器,包括并行的 BS 个乘法单元;每一个乘法单元均与所述滤波系数提供模块和所述待滤波数据提供模块相连接,用于实现所述待滤波数据组中对应的 1 个待滤波数据与所述滤波系数 H(i) 的乘积运算;

累加器,其控制端与比较器相连接,包括并行的 BS 个累加单元;每一累加单元与对应的乘法单元和累加寄存器中寄存单元相连接,用于实现所述乘法单元的当前乘积结果与所述寄存单元的中间数据的累加运算;所述累加器还用于:当接收到所述比较器的输出有效信号时,将 BS 个累加结果作为第n组滤波结果输出;否则,将所述 BS 个累加结果作为中间数据分别输出至累加寄存器中对应的寄存单元;

所述累加寄存器,包括 BS 个寄存单元;每一寄存单元的输入端和输出端分别与相应累加单元的输出端和输入端相连接,用于存放所述累加运算的中间数据;

所述比较器,用于进行运算序号与滤波系数个数 K 的比较运算,当运算序号= K-1 时,向所述累加器发送输出有效信号,随后执行第 n+1 个运算周期,所述运算序号为在第 n 个运算周期中,已经完成的乘积运算或累加运算的次数。

- 2. 根据权利要求 1 所述的 FIR 滤波器, 其特征在于, 所述 n 依次取  $0 \times 1 \times 2 \times 3$ , ……, ceil  $(N_x/BS)-1$ , ceil 为向邻近较大整数取值的符号。

- 3. 根据权利要求 2 所述的 FIR 滤波器, 其特征在于, 所述 i 依次取 K-1、K-2、 ·····、1、0。

- 4. 根据权利要求 3 所述的 FIR 滤波器, 其特征在于, 在每个运算周期中, 所述运算序号从 0 开始, 每次运算增加 1,

所述乘法器和累加器的其中之一,还用于向所述比较器提供所述运算序号;和/或 所述比较器、乘法器和累加器的其中之一,还用于当运算序号< K-1 时,向所述滤波系 数提供模块和所述待滤波数据提供模块发送读使能信号。

- 5. 根据权利要求 4 所述的 FIR 滤波器, 其特征在于, 所述滤波系数提供模块包括:

- 第二存储器,用于存储所述 K 个滤波系数:

- 第二缓存器实体,包含 K'个存储单元, K'≥ K:

第二初始化逻辑单元,与所述第二存储器和第二缓存器实体相连接,用于将所述 K个滤波系数,H[K-1]、H[K-2]、……,H[1] 及 H[0] 从所述第二存储器自前至后依次缓存入所述第二缓存器实体的前 K 个存储单元:

第二读逻辑单元,用于收到读使能信号后,以 K 为周期,按自前至后的顺序依次读取所述第二缓存器实体存储单元中的一个滤波系数,并将该滤波系数发送至所述乘法器。

- 6. 根据权利要求 5 所述的 FIR 滤波器, 其特征在于, 所述 K' = 2BS+1。

- 7. 根据权利要求 5 所述的 FIR 滤波器, 其特征在于,

所述比较器,还用于当运算序号= K-1 时,向所述待滤波数据提供模块发送移位信号; 所述待滤波数据提供模块包括:

第一存储器,用于依次存储 N<sub>v</sub> 个待滤波数据;

第一缓存器实体,包含至少 K'-1+2BS 个存储单元,该 K'-1+2BS 个存储单元用于缓存 待滤波数据;

第一初始化逻辑单元,用于在第 0 个运算周期,对所述第一缓存器实体进行初始化,将地址为 0 ~ K' -2 的存储单元初始化为 0 ;将待滤波数据 X(0)、X(1)、X(2),……,X(2BS-1)从所述第一存储器依次缓存入所述第一缓存器实体的地址为 K' -1 ~ K' -2+2BS 的存储单元;

第一读逻辑单元,其控制端与所述比较器相连接,用于收到所述读使能信号后,以有效偏移地址为起点,按照自前至后的顺序依次读取所述第一缓存器实体中 BS 个存储单元的待滤波数据,并将该 BS 个待滤波数据发送至所述乘法器;

第一移位逻辑单元,其控制端与所述比较器相连接,用于接收到所述比较器的移位信号后,将所述第一缓存器实体中地址为BS至 K'-2+2BS 的存储单元中的待滤波数据前移BS个位置;从所述第一存储器中依次读取BS个待滤波数据依次缓存入所述第一缓存器实体中地址为 K'-1+BS~ K'-2+2BS 的存储单元。

- 8. 根据权利要求7所述的FIR滤波器,其特征在于,所述待滤波数据提供模块中第一缓存器实体包括 4BS 或 5BS 个存储单元。

- 9. 根据权利要求 7 所述的 FIR 滤波器, 其特征在于, 所述 K' = 2BS+1 时, 所述有效偏移地址 = K'-K+ 运算序号。

- 10. 根据权利要求 9 所述的 FIR 滤波器, 其特征在于, 所述滤波系数提供模块中的第一存储器与所述待滤波数据提供模块中的第二存储器为同一存储器;该存储器还用于存储所述第 n 组滤波结果。

- 11. 根据权利要求 1 至 10 中任一项所述的 FIR 滤波器, 其特征在于, 所述滤波结果、滤波系数和待滤波数据的关系如下:

```

Y(0) = H(0)X(0) + H(1)X(-1) + H(2)X(-2) + \cdots + H(K-1)X(-K+1)

```

$Y(1) = H(0)X(1) + H(1)X(0) + H(2)X(-1) + \cdots + H(K-1)X(-K+2)$

$Y(2) = H(0) X(2) + H(1) X(1) + H(2) X(0) + \cdots + H(K-1) X(-K+3)$

. . . . .

$Y(BS-1) = H(0)X(BS-1) + H(1)X(BS-2) + H(2)X(BS-3) + \cdots + H(K-1)X(BS-K)$

$Y(BS) = H(0) X(BS) + H(1) X(BS-1) + H(2) X(BS-2) + \cdots + H(K-1) X(BS-K+1)$

$Y(BS+1) = H(0)X(BS+1)+H(1)X(BS)+H(2)X(BS-1)+\cdots+H(K-1)X(BS-K+2)$

$Y(BS+2) = H(0)X(BS+2) + H(1)X(BS+1) + H(2)X(BS) + \cdots + H(K-1)X(BS-K+3)$

. . . . . .

$Y(2BS-1) = H(0)X(2BS-1) + H(1)X(2BS-2) + H(2)X(2BS-3) + \cdots + H(K-1)X(2BS-K)$

••••

$Y(N_{v}-1) = H(0) X(N_{v}-1) + H(1) X(N_{v}-2) + H(2) X(N_{v}-2) + \cdots + H(k-1) X(N_{v}-K)$

其中,所述H(0)、H(1)、H(2)、·····、H(K-1) 为K 个待滤波系数;

所述 X(-K+1)、X(-K+2)、X(-K+3)、X(BS-K)、 .....、X(0)、X(1)、X(2)、 .....、X(BS-1)、

X(BS)、X(BS+1)、X(BS+2)、……、X(2BS-1)、 $X(N_X-1)$  为  $N_X$  个待滤波数据;

所 述 Y(0)、Y(1)、Y(2)、 ……、Y(BS-1) 为 第 0 组 滤 波 结 果 ;Y(BS)、Y(BS+1)、Y(BS+2)、 …、Y(2BS-1) 为第 1 组滤波结果 ;Y(N<sub>X</sub>-1) 为最后 1 组滤波结果中的最后一个滤波结果。

## 一种有限脉冲响应滤波器

#### 技术领域

[0001] 本发明涉及电子行业数字信号处理技术领域,尤其涉及一种基于乘累加器的有限脉冲响应(Finite Impulse Response,简称 FIR)滤波器。

#### 背景技术

[0002] FIR 滤波器在数字通信系统中有着广泛应用,业界也一直致力于改善其滤波性能。 该滤波器可以用来执行多种工作,比如匹配滤波、噪声隔绝、信道等化等。

[0003] 一般情况下, FIR 滤波器算法可以表示为:

[0004]  $\vec{Y}(k) = \sum_{i=0}^{K-1} \vec{H}(i) \vec{X}(k-i), k=0, 1, 2, \dots, N_{x-1}$ (公式 1)

[0005] 其中, H向量为滤波系数, 其数目为 K个, 包含元素为 H(0)  $\sim$  H(K-1); X向量为待滤波的数据, 其数目为 N<sub>x</sub>个, 包含待滤波数据元素为: X(0)  $\sim$  X(N<sub>x</sub>-1), 算法中使用到的 X向量索引小于 0的部分, 均用零代替; Y向量为滤波输出, 其数目为 N<sub>x</sub>个, 包含元素为 Y(0)  $\sim$  Y(N<sub>x</sub>-1)。现有技术中, 有多种结构及实现方法被提出来, 以加速和简化 FIR 滤波器算法。

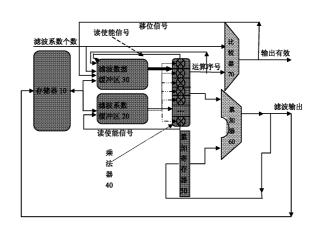

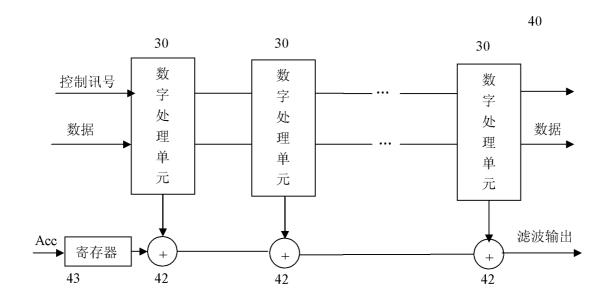

[0006] 中国专利 CN 1525642A公开了一种可重新配置的有限脉冲响应滤波器,该滤波器结构针对固定应用场合有较高的效率,其构造如图 1 所示。参照图 1,该滤波器的工作过程如下:根据应用场合固定滤波系数个数 K,而后根据该 K 个滤波器系数设计 K 个数字处理单元, K 个滤波系数预先存储在数字处理单元中,当待滤波数据从图 1 中左边输入时,每次可以完成 K 个待滤波数据和 K 个滤波系数的乘法运算,然后再横向累加,得到 1 个滤波结果,从图 1 所示 FIR 滤波器的右边输出。

[0007] 在实现本发明的过程中,申请人意识到现有技术 FIR 滤波器存在如下技术缺陷:

[0008] 1) 当滤波系数 K 数目较大时,现有技术 FIR 滤波器一般是将各个滤波系数同待滤波数据相乘,得到子结果,这个过程是并行完成,但是之后将各个子结果相加得到滤波结果时,该累加所需时间直接取决于滤波系数个数,在滤波系数数目较大的时候,滤波结果输出的关键路径很长,严重影响其工作效率;

[0009] 2) 数字处理单元个数受限于滤波系数个数,必须确定了应用场合中滤波系数的个数后,才能固定数字处理单元的个数,缺乏应用灵活性。即当滤波器系统固定后,该滤波器系统仅适用于一种应用场合,该场合所需滤波系数个数固定;

[0010] 3) 在一维滤波应用中,待滤波数据存在着局部性原理,加载重复的数据使得待滤波数据的使用效率很低,另外重复的访问存储器一方面会有较大的时间开销,另一方面会增大系统的功耗。

#### 发明内容

[0011] (一)要解决的技术问题

[0012] 为解决上述的一个或多个问题,本发明提供了一种有限脉冲响应 FIR 滤波器,以提高 FIR 滤波器的工作效率。

[0013] (二)技术方案

根据本发明的一个方面,提供了一种有限脉冲响应 FIR 滤波器。该 FIR 滤波器包 [0014] 括:滤波系数提供模块,用于预存K个滤波系数:在第n个运算周期,接收到读使能信号后, 提供1个滤波系数H(i):待滤波数据提供模块,用于预存N<sub>v</sub>个待滤波数据:在第n个运算周 期,接收到读使能信号后,提供1个待滤波数据组,该待滤波数据组包括BS个待滤波数据: X(nBS-i),X(nBS-i+1), ······,X[(n+1)BS-i-1], 当待滤波数据的向量索引小于 0 时,该待滤 波数据以 0 代替;乘法器,包括并行的 BS 个乘法单元;每一个乘法单元均与滤波系数提供 模块和待滤波数据提供模块相连接,用于实现滤波系数 H(i) 与待滤波数据组中的1个待滤 波数据的乘积运算;累加器,其控制端与比较器相连接,包括并行的BS 个累加单元;每一累 加单元与对应的乘法单元和累加寄存器中寄存单元相连接,用于实现乘法单元的当前乘积 结果与寄存单元的中间数据的累加运算;累加器还用于:当接收到比较器的输出有效信号 时,将BS 个累加结果作为第n组滤波结果输出;否则,将BS 个累加结果作为中间数据分别 输出至累加寄存器中对应的寄存单元;累加寄存器,包括 BS 个寄存单元;每一寄存单元的 输入端和输出端分别与相应累加单元的输出端和输入端相连接,用于存放累加运算的中间 数据:比较器,用于进行运算序号与滤波系数个数K的比较运算,当运算序号=K-1时,向累 加器发送输出有效信号,随后执行第 n+1 个运算周期,运算序号为在第 n 个运算周期中,已 经完成的乘积运算或累加运算的次数。

[0015] (三)有益效果

[0016] 从上述技术方案可知,本发明 FIR 滤波器具有以下有益效果:

[0017] 1)并行计算的高效率,本发明采用BS个并行的乘法单元,可以同时进行BS个乘法运算,同时将BS个乘法结果同相应的寄存器中值并行进行BS个加法运算,从而大大提高了运算效率,节约运算时间,并且所有的控制信号均是数字信号,避免了采用延迟单元等模拟单元所带来的运算不准确性,提高了运算精度;

[0018] 2) 可重构性,本发明在缓存空间尺寸范围内的滤波系数个数情况下,均取得高效的滤波效果,即使当滤波系数的个数发生变化时,只要其在缓存空间的范围之内,就不用重新更改相应硬件,从而实现了相当好的重构性;

[0019] 3) 待滤波数据高利用率,本发明通过在整个算法层面分析,使用待滤波数据缓存器和滤波系数缓存器结构,充分利用了待滤波数据局部性原理,没有重复加载待滤波数据的现象,并且每访问一次存储器,可得出 BS 个结果,减少存储器访问次数,从而达到了"一次读取,多次计算"的效果,进而降低了整个设计的功耗。

#### 附图说明

[0020] 图 1 为现有技术 FIR 滤波器的结构示意图:

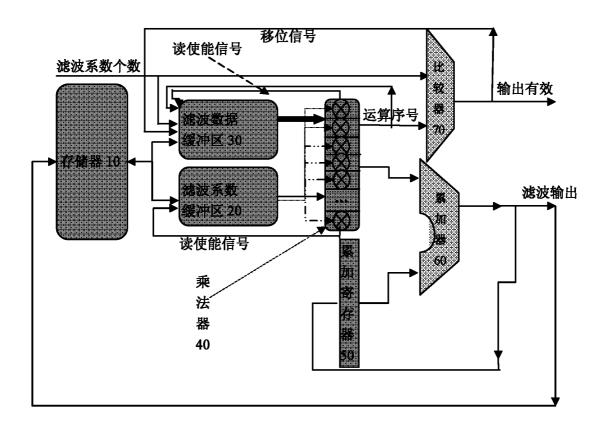

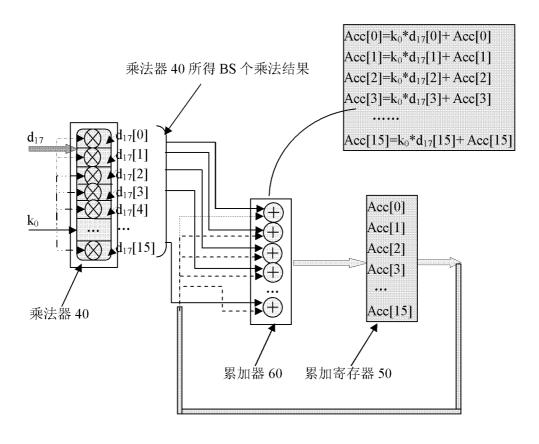

[0021] 图 2 为本发明实施例 FIR 滤波器的结构示意图;

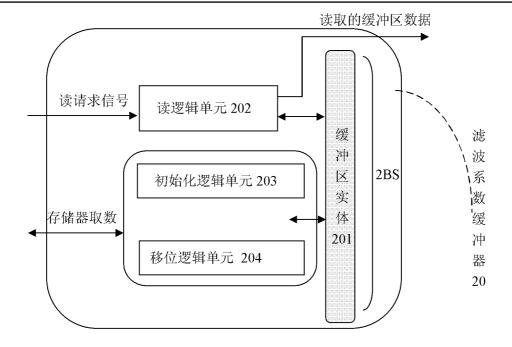

[0022] 图 3 为本发明实施例 FIR 滤波器中滤波系数缓存器的示意图;

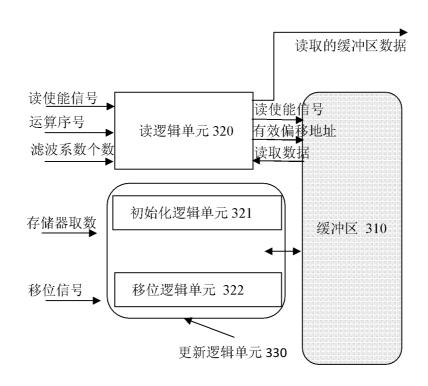

[0023] 图 4 为本发明实施例 FIR 滤波器中待滤波数据缓存器的示意图;

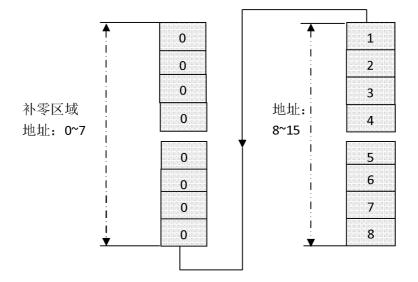

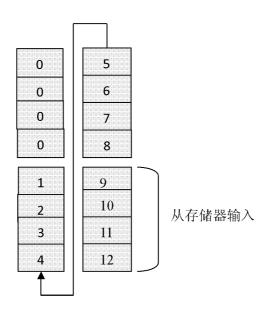

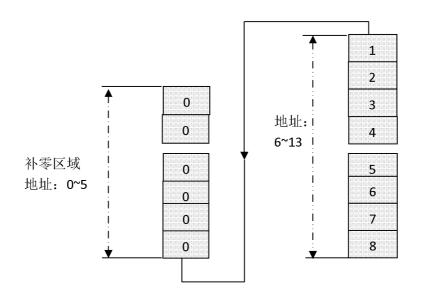

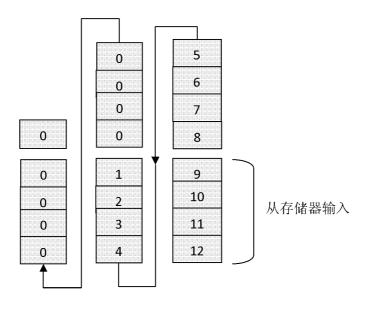

[0024] 图 5a 为本发明实施例 FIR 滤波器在 BS = 4 时待滤波数据缓存器存储空间为 4BS 下编码和初始化后的示意图;

[0025] 图 5b 为如图 4a 所示待滤波数据缓存器在移位后的示意图;

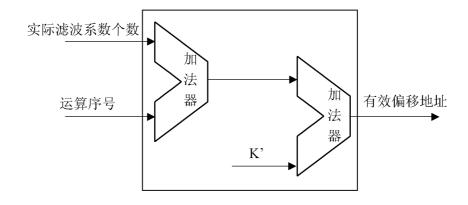

[0026] 图 6 为本发明实施例 FIR 滤波器有效偏移地址产生图的示意图;

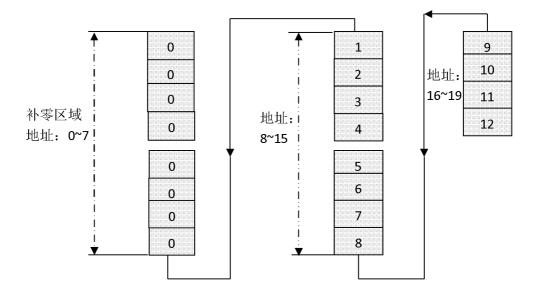

[0027] 图 7a 为本发明实施例 FIR 滤波器在 BS = 4 时待滤波数据缓存器存储空间为 5BS 下编码和初始化后的示意图:

[0028] 图 7b 为如图 6a 所示待滤波数据缓存器在移位后的示意图:

[0029] 图 8a 为本发明实施例 FIR 滤波器中滤波系数在存储器中存储的示意图;

[0030] 图 8b 为本发明实施例 FIR 滤波器中滤波系数在滤波系数缓存器中存储的示意图:

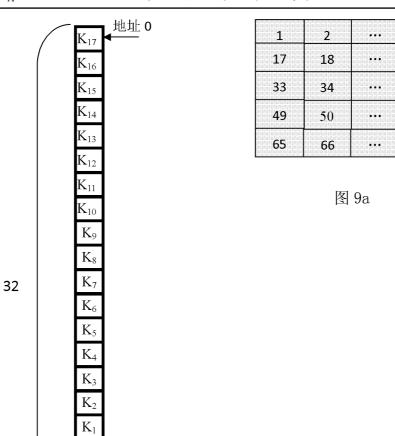

[0031] 图 9a 为本发明实施例 FIR 滤波器中待滤波数据在存储器中存储的示意图:

[0032] 图 9b 为本发明实施例 FIR 滤波器中待滤波数据在待滤波数据缓存器中存储的示意图;

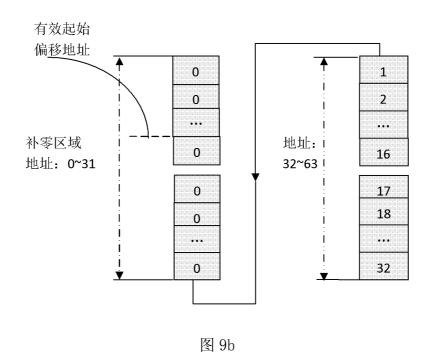

[0033] 图 10a 为本发明实施例 FIR 滤波器进行第 1 次乘累加运算的示意图;

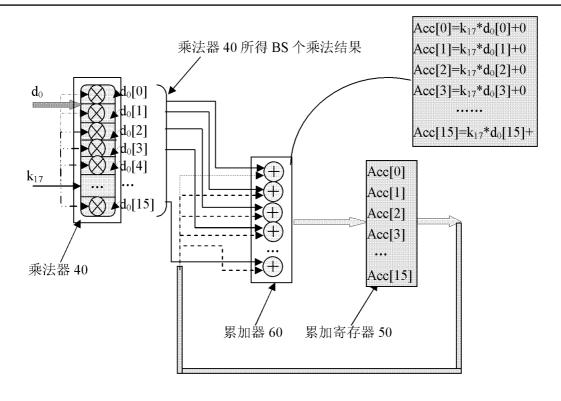

[0034] 图 10b 为本发明实施例 FIR 滤波器进行第 2 次乘累加运算的示意图;

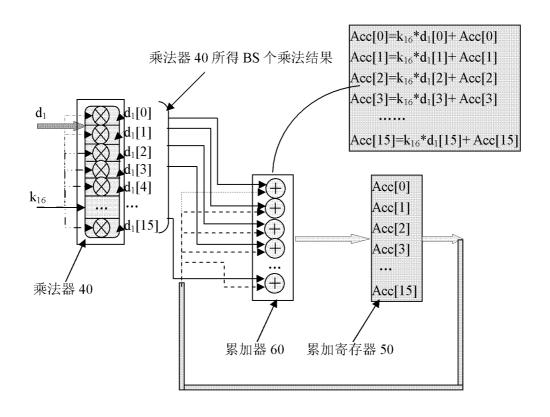

[0035] 图 10c 为本发明实施例 FIR 滤波器进行第 18 次乘累加运算的示意图;

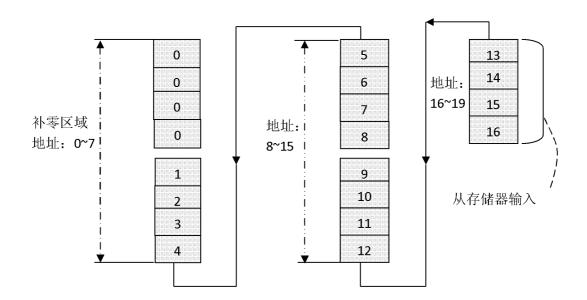

[0036] 图 11A 为当 K' = BS+3 时本发明实施例待滤波数据缓存器初始化后的数据存储的示意图;

[0037] 图 11B 为图 11A 所述待滤波数据缓存器移位后的数据存储的示意图;

[0038] 图 12A 为当 K' = 3BS+2 时本发明实施例待滤波数据缓存器初始化后的数据存储的示意图:

[0039] 图 12B 为图 12A 所述待滤波数据缓存器移位后的数据存储的示意图。

#### 具体实施方式

[0040] 为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。虽然本文可提供包含特定值的参数的示范,但应了解,参数无需确切等于相应的值,而是可在可接受的误差容限或设计约束内近似于所述值。

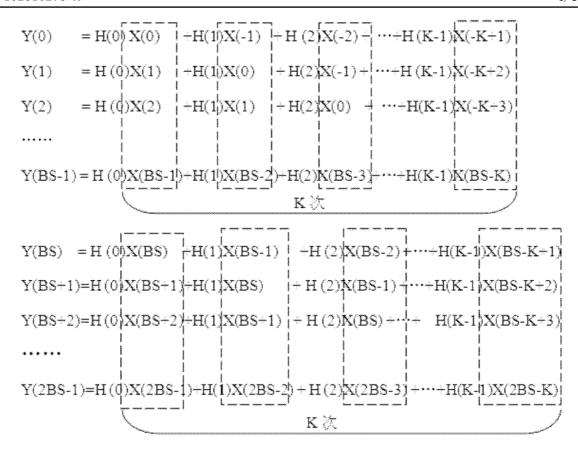

[0041] 申请人发现,可以将公式1中FIR滤波器的算法展开为如下的结果:

[0042]

\*\*\*\*\*

$Y(N_x-1) = H(0)X(N_x-1) + H(1)X(N_x-2) + H(2)X(N_x-2) + \cdots + H(k-1)X(N_x-k)$

[0043] 对于如上所示的 FIR 滤波器算法展开结果,滤波系数使用具有如下规律:

[0044] (1) 就每一个虚线框所在的列来说,每次乘法器用一个滤波系数和虚线框内 BS 个 待滤波数据进行运算,这个过程的 BS 个乘法可以为并行运算;

[0045] (2) 并行后的结果再进行累加,累加过程是如上所示自右向左,累加 K 次后即可得出 Y(0)  $\sim$  Y(BS-1) 共 BS 个结果。其中,每得出 BS 个结果,分别使用滤波系数 H(K-1)、H(K-2)、H(K-3)、……、H(1)、H(0)。

[0046] 因此,对滤波系数缓存器有两点要求:1、每次读取返回一个滤波系数;2、相隔 K 次读取,返回的值一样。按照上述的结果,滤波系数的个数为 K,运算数据的个数为 BS。

[0047] 对于如上所示的 FIR 滤波器算法展开结果, 待滤波数据使用具有如下规律:

[0048] (1) 对于左右相邻的虚线框,其使用待滤波数据仅有一个不同。

[0049] (2) 上下相邻 BS 个滤波结果运算中,有 BS 个待滤波数据不再使用,同时新使用 BS 个待滤波数据。例如,计算 Y (BS)  $\sim$  Y (2BS-1) 时,待滤波数据 X (-K+1)  $\sim$  X (BS-K) 不再使用,待滤波数据 X (BS-K+1)  $\sim$  X (BS-1) 继续使用,同时新增加了待滤波数据 X (BS)  $\sim$  X (2BS-1) 的使用。

[0050] (3) 待滤波数据 X 向量,其索引值小于零的部分,均由零代替。即上式中的 X(-1)、X(-2)、……、X(-K+1) 均为零。

[0051] 根据上述规律,可以设计一种新型的待滤波数据缓存器,该待滤波数据缓存器至少满足以下四点要求:1、每次读取缓存器可以返回 BS 个待滤波数据:2、相邻两次缓存器的

读取,在返回的BS个待滤波数据里面,仅有一个值不同;3、每完成K次运算,即产生了BS个滤波结果后,该缓存器有一个整体的更新,该更新将最开始使用的BS个待滤波数据舍弃,新加载进来BS个在存储器中的待滤波数据;4、缓存器提供相应的补零区域,有效零个数为K-1。

[0052] 在上述滤波系数和待滤波数据规律的技术上,申请人提出一种 FIR 滤波器,以提高滤波系数和待滤波数据的使用效率,减少对存储器的读写次数,提高运算速度。

[0053] 在本发明的一个示例性实施例中,提出了一种 FIR 滤波器。图 2 为本发明实施例 FIR 滤波器的结构示意图。如图 2 所示,本实施例 FIR 滤波器包括:滤波系数缓存器 20、待滤波数据缓存器 30、乘法器 40、累加寄存器 50、累加器 60 和比较器 70。该 FIR 滤波器的外围部件还包括存储器 10。

[0054] 滤波系数缓存器 20,用于预存 K 个滤波系数;在第 n 个运算周期,接收到读使能信号后,提供 1 个滤波系数 H(i)。

[0055] 待滤波数据缓存器 30,用于预存  $N_x$  个待滤波数据;在第 n 个运算周期,接收到读使能信号后,提供 1 个待滤波数据组,该待滤波数据组包括 BS 个待滤波数据:X(nBS-i), X(nBS-i+1), ……,X[(n+1)BS-i-1],当待滤波数据的 X 向量索引小于 0 时,该滤波数据以 0 代替。

[0056] 乘法器 40,包括并行的 BS 个乘法单元;每一个乘法单元均与滤波系数缓存器 20 和待滤波数据缓存器 30 相连接,用于实现滤波系数 H(i)与待滤波数据组中的 1 个待滤波数据的乘积运算,得到 1 个乘法结果。

[0057] 累加器 60,其控制端与比较器相连接,包括并行的 BS 个累加单元;每一累加单元与对应的乘法单元和累加寄存器中寄存单元相连接,用于累加所述乘法单元的当前乘积结果与寄存单元的中间数据。当接收到比较器的输出有效信号时,该累加器将 BS 个累加结果作为第 n 组滤波结果输出;否则,将该 BS 个累加结果作为中间数据分别输出至累加寄存器中对应的寄存单元。

[0058] 累加寄存器 50,包括独立的 BS 个寄存单元,每一寄存单元的输入端和输出端分别与相应累加单元的输出端和输入端相连接,用于存放累加运算的中间数据。

[0059] 比较器 70,用于比较由乘法器 40 传递来的运算序号与滤波系数个数 K 的关系,当运算序号 < K-1 时,向滤波系数缓存器和待滤波数据缓存器发送读使能信号,当运算序号 = K-1 时,向累加器发送输出有效信号。事实上,该运算序号也可以由累加器 60 或累加寄存器 50 传递至比较器,其原理与此类似,同样在本发明的保护范围之内。其中,运算序号为在进行某一组的 BS 的结果数据计算过程中,已经完成的乘积运算或累加运算的次数,该值从 0 开始计数,最大值为 K-1。同时,当该组 BS 的结果数据计算完毕,下一组 BS 的结果数据的计算过程中,运算序号重新从 0 开始计数。

[0060] 需要说明的是, n 依次取 0.1.2.3, ……, ceil  $(N_x/BS)-1$ , ceil 为向邻近较大整数取值的符号, ceil  $(N_x/BS)-1$  组滤波结果作为  $N_x$  个待滤波数据的滤波结果。

[0061] 此外,本实施例中待滤波数据和滤波系数选取的原则在于,不同次的读使能信号对应提供的滤波系数不同,并且不同次的读使能信号对应的待滤波数据组不同。一般说来,可以逐一选择滤波系数和待滤波数据组,只要保证 K 次运算不相互重复即可。当然,对于如FIR 滤波器的算法展开结果来讲,有两种惯用的计算方法,一种方法是自右至左依次计算,

另一种方法是自左至右依次计算。优选的,对于 FIR 滤波器的算法展开结果,自右至左依次计算,即 i 依次取 K-1、K-2、……、1、0(将在下文中详细说明)。

[0062] 为了能够更加清楚了理解本实施例,现对其时序控制信号的产生与输出进行说明。如图 2 所示,比较器的输出有效信号一方面用来指示当前已经完成 BS 个滤波结果,即当前累加器 60 的输出有效,另一方面用来指示当前输出到待滤波数据缓存器 30 的移位信号有效(将在下文中详细说明)。此外,由乘法器 40 输出到滤波系数缓存器 20 的读使能信号,用来指示当前乘法器 40 需要读取滤波系数缓存器 20;由乘法器 40 输出到待滤波数据缓存器 30。当然,该读存器 30 的读使能信号,用来指示当前乘法器 40 需要读取待滤波数据缓存器 30。当然,该读使能信号也可以由比较器或累加器下发至滤波系数缓冲器和待滤波数据缓冲器,即比较器、乘法器和累加器的其中之一,还用于当运算序号 < K-1 时,向所述滤波系数提供模块和所述待滤波数据提供模块发送读使能信号。

[0063] 从本实施例可以看出,不同于现有技术中的 FIR 滤波器,本发明采用 BS 个并行的乘法单元,可以同时进行 BS 个乘法运算,同时将 BS 个乘法结果同相应的寄存器中值并行进行 BS 个加法运算,从而大大提高了运算效率,节约运算时间,并且所有的控制信号均是数字信号,避免了采用延迟单元等模拟部件所带来的运算不准确性,提高了运算精度。

[0064] 采用本实施例中的并行乘法单元及其配套加法器和寄存器,可以同时进行 BS 个并行运算,该并行运算为产生 BS 个滤波结果的一部分运算,采用这种形式的并行,使得运算部件的数量独立于滤波系数个数,当滤波系数增加时,复用设计中的并行乘法单元及其配套加法器和寄存器,具有高度的灵活性。

[0065] 本实施例 FIR 滤波器采用滤波系数缓存器和待滤波数据缓存器。事实上,也可以采用能够实现待滤波数据提供功能的其他存储器件,如寄存器等。为了尽可能减少对存储器的读取,提高运算速度和效率,对于滤波系数,本发明采用存储器和缓存器相互结合的方式,将滤波系数从存储器中按顺序存入缓存器中,以滤波系数个数 K 为周期,每次输出一个滤波系数。具体技术方案如下:

[0066] 本实施例中,滤波系数缓存器 20,用于从存储器 10 中读取滤波系数,置于缓存器实体内,每次滤波器运算按顺序读取 1 个滤波系数 H(i)。图 3 为本发明实施例 FIR 滤波器中滤波系数缓存器的示意图。如图 3 所示,该滤波系数缓存器 20 包括一个缓存器实体 201、一个读逻辑单元 202、一个初始化逻辑单元 203 和一个移位逻辑单元 204。其中:

[0067] 缓存器实体 201,缓存用于运算的滤波系数,其大小与运算单元的尺寸 (BS) 有关,此处缓存器存储单元个数为 2BS+1,且自上到下编址为 0 ~ 2BS。

[0068] 读逻辑单元 202 用于对滤波系数缓存器的读操作,以滤波系数个数(K)为周期,按顺序返回一个滤波系数。

[0069] 初始化逻辑单元 203 用于对缓存器实体的初始化。即从存储器取数对缓存器实体 201 进行赋值。

[0070] 从上述滤波系数缓存器 20 的结构可以看出,本发明运算单元个数 BS 与滤波系数个数 K 不存在必然的关系。在运算单元个数 BS 一定的情况下,如果滤波系数个数 K 发生变化,则不需要更改内部运算单元个数或尺寸,只要该滤波系数个数 K 在滤波系数缓存器的存储空间范围内,就完全可以满足运算的需要,具有高度灵活性,从而使得本发明具有良好的可重构性。以滤波系数缓存器的大小为 2BS+1 来讲,可适应 2BS+1 个滤波系数范围内的

滤波运算。为了便于理解,在下文的说明中,以滤波系数缓冲器所能支持的最大滤波系数个数尺寸为 K'为例。

[0071] 本实施例中,滤波系数缓冲器是为满足滤波器实现过程中对滤波系数的要求而设计的,其功能为提供滤波系数,其实现形式可能多样,比如可以采用 2BS+1 个寄存器实现,而不需要额外逻辑开销,但是在每次乘积运算中,乘法器需要控制从哪个寄存器取所需系数。

[0072] 进一步,为了提高待滤波数据的提高效率,本发明还对待滤波数据的提供部件进行了改进,本实施例中,待滤波数据缓存器 30,用于从存储器 10 中读取待滤波数据组,置于待滤波数据缓存器实体内,每次滤波器运算读取待滤波数据组  $d_K$ ,其中, $d_K$  为一向量【 $d_K$ [0], $d_K$ [1], ……, $d_K$ [BS-1]】,FIR 滤波器算法展开式中  $d_K$  向量索引小于 0 的部分,如 X[-1],均用 0 代替。该缓存器大小为 4BS,其中 BS 为乘法器的运算尺寸,即可以同时进行的乘法运算数目。

[0073] 图 4 为本发明实施例 FIR 滤波器中待滤波数据缓存器的示意图。如图 4 所示,该待滤波数据缓存器包括待滤波数据缓存器实体 310、读逻辑单元 320、更新逻辑单元 330。其中:

[0074] 缓存器实体 310 缓存用于运算的待滤波数据。其大小与运算单元需求的尺寸 (BS) 有关,此处大小为 4BS 大小,并且编址为  $0 \sim 4BS-1$ 。

[0075] 读逻辑单元 330 用于读缓存器的待滤波数据。其输入信号为读使能信号、运算序号和滤波系数个数,输出信号包括向缓存器实体 10 发出有效偏移地址,得到 BS 尺寸的待滤波数据,并将该待滤波数据输出。

[0076] 其中有效偏移地址需要根据运算序号、读使能信号和滤波系数个数产生。对应关系为:当读使能信号有效时,有效偏移地址= K'-K+运算序号。其中运算序号是由运算单元(乘法单元)按照读缓存的顺序,发送的读取号,该运算序号从0开始,每次增加1。对于本实施例来讲,滤波系数缓存器实体的大小为2BS+1,该有效偏移地址=2BS+1-K+运算序号。[0077] 更新逻辑单元320用于更新缓存器实体的待滤波数据内容,该结构包括一个初始化逻辑单元321和一个移位逻辑单元322。其中:

[0078] 初始化逻辑单元在运算部件工作前对缓存器实体 10 的前期操作。用于对缓存器实体的初始化,其中地址为  $0\sim 2BS-1$  的部分初始化为 0,地址  $2BS\sim 4BS-1$  部分从存储器里面取值初始化。

[0079] 移位逻辑单元 322 用于对存储区实体待滤波数据的整体移位,即当输入信号移位信号有效时,移位逻辑单元开始工作。

[0080] 先假定待滤波数据缓存器配合的一维滤波所支持的最大滤波系数个数 K' = 2BS+1,则本待滤波数据缓存器实体大小至少为 4BS 大小,同时假定运算单元尺寸,即 BS = 4,实际滤波系数个数为 K = 6。

[0081] 结合上述假设可知,K' = 9,待待滤波数据缓存器实体大小> = 4BS = 16,K = 6。下面首先以数缓存器实体大小为 4BS = 16 为例对本发明做进一步说明。

[0082] 在使用的开始阶段,本实施例需要先进行初始化,此时初始化逻辑单元 201 工作,将数缓存器地址  $0 \sim 7$  的部分初始化为 0,将地址  $8 \sim 15$  的部分初始化为特定的值,该值从存储器取得,每次从存储器可以取 BS = 4 个待滤波数据,共需要取 2 次。缓存器编址及初

始化后的情况如图 5a 所示。

[0083] 初始化完毕后,运算部件即采用图 2 所示中的乘法器需要读取该缓存器,此时读逻辑单元 330 开始工作,根据输入的运算序号、读使能信号以及最大支持滤波系数个数和实际滤波系数个数信号,产生有效偏移地址,从而读出正确位置的待滤波数据。

[0084] 本实施例中,由于每产生 BS = 4 个待滤波数据需要读取 K = 6 次缓存,故运算序号为一串  $\{0.1,2.3.4.5\}$  的循环码。当产生第一组 BS = 4 个滤波结果数据时,有效偏移地址=  $\{3.4.5.6.7.8\}$ 。该有效偏移地址产生图如图 6 所示。故此时前 6 次读取待滤波数据缓存器返回的待滤波数据分别为  $\{0.0.0.0.0\}$ ,  $\{0.0.0.0.1\}$ ,  $\{0.0.1.2\}$ ,  $\{0.1.2.3\}$ ,  $\{1.2.3.4\}$ 。

[0085] 当图 2 中的乘法器运算 K = 6 次后,即可得出前 BS = 4 个结果值,之后需要更新缓存器实体 310 的值,即从存储器里面取值。此时图 2 中 FIR 滤波器中输出给待滤波数据缓存器 30 的移位信号有效,缓存器会有一个整体的移位,移位的幅度为 BS = 4。移位后缓存器待滤波数据如图 5b 所示。

[0086] 此时已经得出了 BS 个滤波输出数据,并且缓存器已经做好相应待滤波数据的更新,配合运算部件进行下面 BS 个结果待滤波数据的运算,期间读缓存器和更新缓存机制不变。

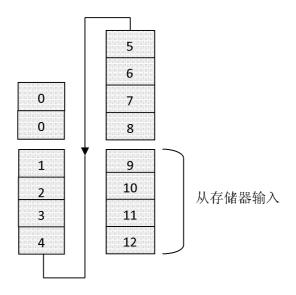

[0087] 上述实施例是缓存器大小为 4BS 的情况,实际上本缓存器不仅仅限于 4BS 大小。在 K' = 2BS+1 的前提下,下面以缓存器实体 10 为 5BS 大小为例,详细介绍本发明。

[0088] 当缓存器实体 310 大小为 5BS 时,同样待滤波数据在存储器中的分布如图 5a 所示,实际滤波系数个数(小于或等于 2BS)为 K=6,则缓存器实体的编址为  $0\sim19$ 。

[0089] 图 7a 为待滤波数据缓存器大小为 5BS 时,初始化完毕后,缓存器实体中的待滤波数据。此时相比大小为 4BS 的缓存器,初始化完毕后多缓存了 BS = 4 个待滤波数据。这些并不影响本发明的读逻辑单元 330,它同样根据输入的运算序号、读使能信号以及滤波系数个数信号,产生有效偏移地址,从而读出正确位置的待滤波数据。

[0090] 同样的,每产生第一组BS = 4个滤波结果数据,有效偏移地址分别 =  $\{3.4.5.6.7.8\}$ 。该有效偏移地址产生图如图 6 所示。故此时前 6 次读取待滤波数据缓存器返回的待滤波数据分别为  $\{0.0.0.0\}$ ,  $\{0.0.0.0\}$ ,  $\{0.0.0.1\}$ ,  $\{0.0.1.2\}$ ,  $\{0.1.2.3\}$ ,  $\{1.2.3.4\}$ 。

[0091] 当图 2 中的乘法器运算 K = 6 次后,即可得出前 BS = 4 个结果值,之后需要更新 待滤波数据缓存器实体 310 的值,即从存储器里面取值。此时图 2 中输出给待滤波数据缓存器 30 的移位信号有效,缓存器会有一个整体的移位,移位的幅度为 BS = 4。移位后缓存器待滤波数据如 7b 所示。

[0092] 此时已经得出了 BS 个滤波输出数据,并且缓存器已经做好相应待滤波数据的更新,配合运算部件进行下面 BS 个结果数据的运算,期间读缓存器和更新缓存机制不变。

[0093] 从上述待滤波数据缓存器 30 的结构可以看出,其充分考虑到算法中数据重复利用现象,在存储器加载特定数目数据后,进行充分运算,根据算法要求,所有使用到该部分待滤波数据的运算都完成后,才做待滤波数据缓存器的更新,之后该部分待滤波数据在整个算法实现过程中不会再次被加载,这样提高了待滤波数据利用率,减少了访问存储器的次数,解决了处理器做一维滤波算法时对处理器强劲供数能力的需求,进而降低了整个设计的功耗。

[0094] 本实施例中,可以简化待滤波数据缓冲器的功能,将待滤波数据缓冲器要做的事情移交给运算单元(乘法单元或累加单元)去做,比如可以简化数据缓冲器的读逻辑,将该部分的有效地址产生移交给读逻辑单元去做。但是初始化逻辑和更新逻辑是必不可少的。总之,由于本发明滤波器对数据的需求,所以设计了该缓冲器。可以将滤波器对数据的要求看作需求规范,而本待滤波数据缓冲器为一种最有可能的实现。其它的实现本规范全部或者部分的时序逻辑,都可以看作是本发明的待滤波数据缓冲器。

[0095] 此外,本实施例待数据缓冲器针对不同滤波系数个数的应用场合,能够根据算法需求智能补零,极大方便了程序员进行算法实现,而不需要考虑针对不同系数长度进行合适数目的补零操作。

[0096] 当然,也可以采用其他的待滤波数据提供方式,如将待滤波数据缓冲器分为 BS 个子缓冲器,将第 n 个运算周期中每一个滤波系数相对应的 BS 个待滤波数据均存储至 BS 个子缓冲器的其中之一。在每次乘法运算中,从子缓冲器中读取全部的待滤波数据至乘法器。当然,这种待滤波数据提供方式耗费的内存较大,读取效率较低。

[0097] 以下用一具体的场景为例对本发明做详细说明如下:在本实施例中,乘法器的运算尺寸 BS = 16,即每次该乘法器可以进行 16 对数据相乘,则相应的,滤波系数缓存器的大小为 2\*BS+1 = 33 个待滤波数据宽度,待滤波数据缓存器的大小为 4\*BS = 64 个待滤波数据宽度,乘法器具有并行的 16 个乘法单元,累加器具有并行的 16 个累加单元。累加寄存器的宽度为 BS = 16 个数据宽度。此处不限定数据类型,可以是 64bit、32bit、16bit 和 8bit 数据类型。

[0098] 事实上,在数字信号领域的其它算法中,比如卷积和相关运算,其运算特征同 FIR 滤波器实现一样,均为数据和系数相乘,然后累加得出一个结果,本发明提供的滤波器及其系数缓冲器、数据缓冲器同样可以运用到该算法实现中。

[0099] 假设滤波器的滤波系数个数 K = 18,假设其在存储器中分布如 8a 所示。在运算开始前,需要进行滤波系数缓存器 20 和待滤波数据缓存器 30 的初始化。初始化完毕后,滤波系数缓存器 20 内存储了滤波所需的 18 个滤波系数,如图 8b 所示。

[0100] 完成缓存器的初始化后,乘法器开始对相应待滤波数据进行运算,为了充分利用待滤波数据缓存器中的待滤波数据,乘法器每得到一次有效结果,共进行 K = 18 次运算,每次运算时调用滤波系数缓存器 20 和待滤波数据缓存器 30 一次。

[0101] 乘法器 40 每次对滤波系数缓存器 20 的调用可以返回一个数据。假设对滤波系数缓存器 20 的 K = 18 次调用可以返回  $k_{17}$ ,  $k_{16}$ , …,  $k_2$ ,  $k_1$ ,  $k_0$ , 其中  $k_0$  的宽度为 1 个数据的宽度。 $k_{17}$ ,  $k_{16}$ , …,  $k_2$ ,  $k_1$ ,  $k_0$  分别对应着 FIR 滤波器算法展开式中的 H(K-1), H(K-2), …, H(2), H(1), H(0), 且 K = 18。

[0102] 每次对待滤波数据缓存器 30 的调用可以返回 BS = 16 个待滤波数据,乘法器 40 对待滤波数据缓存器 30 的 K = 18 次调用可以返回  $d_0$ ,  $d_1$ ,  $d_2$ ……,  $d_{17}$ , 它们分别对应着 FIR 滤波器算法展开式中上半部分自右向左的 K = 18 个方框中的待滤波数据。所以  $d_0 \sim d_{17}$  的宽度为 BS = 16 个待滤波数据的宽度,在后面描述中均以一维数组的形式表征,即  $d_0$ [0]  $\sim d_0$ [15] 表示  $d_0$ ,  $d_{17}$ [0]  $\sim d_{17}$ [15] 表示  $d_{17}$ 。 待滤波数据缓存器的实现结构保证了其所提供的待滤波数据为滤波算法需要的待滤波数据。

[0103] 具体说来,假设待滤波数据在存储器和待滤波数据缓存器 30 的分布分别如 8a 和

8b 所示。则  $d_0[0] \sim d_0[15] = \{0,0,0, \dots, 0\}$ 、 $d_1[0] \sim d_1[15] = \{0,0,0, \dots, 0\}$ 、…、  $d_{17}[0] \sim d_{17}[15] = \{1,2,3, \dots, 16\}$ 。

[0105] 图 10a 至图 10c 描述了上述经过 K = 18 次运算,得出 BS 个结果的过程,实际上也是对 FIR 滤波器展开算法的 K 次自右向左累加的一个硬件实现描述。

[0106] 其中图 10a 描述了第 1 次乘累加的过程,此时累加寄存器 50 中的值为 0,经累加计算后,滤波系数  $k_{17}$  和  $d_0$  的各元素乘积的结果值放入累加寄存器,即完成了  $k_{17}d_0[0]$ 、 $k_{17}d_0[1]$ 、 $k_{17}d_0[2]$ 、……、 $k_{17}d_0[15]$  的运算。

[0107] 图 10b 为第 2 次乘累加的过程,此时乘法器 40 输出的结果为  $k_{16}$  和  $d_1$  各元素的乘积,累加器将该结果和上次累加结果(当前累加寄存器 50 中的值)相加,得到结果  $k_{17}d_0[0]+k_{16}d_1[0]$ 、 $k_{17}d_0[1]+k_{16}d_1[1]$ 、 $k_{17}d_0[2]+k_{16}d_1[2]$ 、……、 $k_{17}d_0[15]+k_{16}d_1[15]$ ,并放入累加寄存器 50 中;剩余  $k_{15}\sim k_1$  与待滤波数据  $d2\sim d16$  的运算过程类似。

[0108] 图 10c 为第 18 次乘累加的过程,此时仍是将乘法器 40 的结果与累加寄存器 50 相加。经过上述 18 次运算,可以得出 BS = 16 个结果,相当于做了如下等式序列的累加:

[0109]  $k_{17}d_0[0]+k_{16}d_1[0]+\cdots+k_2d_{15}[0]+k_1d_{16}[0]+k_0d_{17}[0]$ ,

[0110]  $k_{17}d_0[1]+k_{16}d_1[1]+\cdots+k_2d_{15}[1]+k_1d_{16}[1]+k_0d_{17}[1]$ ,

[0111]  $k_{17}d_0[2]+k_{16}d_1[2]+\cdots+k_2d_{15}[2]+k_1d_{16}[2]+k_0d_{17}[2]$ ,

[0112] .....

[0113]  $k_{17}d_0[15]+k_{16}d_1[15]+\cdots+k_2d_{15}[15]+k_1d_{16}[15]+k_0d_{17}[15]$ ,

[0114] 上述序列即是滤波结果  $Y(0) \sim Y(15)$  的表达式。

[0115] 若输入待滤波数据没有全部进行滤波运算,则需要更新待滤波数据缓存器 30,即 在每计算完毕 BS 个待滤波数据后,发送给待滤波数据缓存器一个移位信号,待滤波数据缓存器在整体移位的同时,从存储器里面重新取值。之后重复乘法器 40 和累加器 60 的协同运算过程,直到待滤波数据全部计算完毕。

[0116] 特别说明的是,如果待滤波数据个数  $N_x$  不能被 BS 整除,整个运算过程保持不变,但是在最后一次运算得出的 BS 个结果中,只有  $N_m$  个有效滤波结果数据,  $N_m$  为  $N_x$  除以 BS 所得的余数。最后一次将数据写回存储器时,只将该  $N_m$  个有效结果写回。

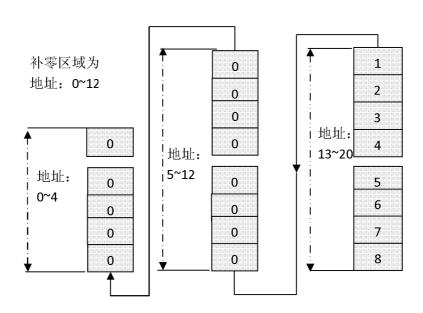

[0117] 在上述各个实施例中,K' = 2BS+1,K' 为本滤波数据提供装置所应用到的滤波器所能支持的最大数目滤波系数尺寸,因此,待滤波数据提供装置中缓存器实施的尺寸大小为 K'-1+2BS = 4BS。本领域技术人员应当可以理解,K' 不仅仅限定于 2BS+1,下面分别以 K' = BS+3 和 K' = 3BS+2 为例进行说明。如下所示:

[0118] 当 K' = BS+3 时,其实施例如下:此时缓冲器大小至少为 3BS+2。同时依然假定运算单元尺寸,即 BS = 4,实际滤波系数个数为 K = 6,此时 K' = 7,缓冲区大小至少为 14。

[0119] 在使用的开始阶段,本实施例需要先进行初始化,此时初始化逻辑单元 201 工作,将数缓存器地址  $0 \sim 5$  的部分初始化为 0,将地址  $6 \sim 13$  的部分初始化为特定的值,该值从存储器取得,每次从存储器可以取 BS = 4 个待滤波数据,共需要取 2 次。缓存器编址及初

始化后的情况如图 11A 所示。

[0120] 初始化完毕后,运算部件即采用图 2 所示中的乘法器需要读取该缓存器,此时读逻辑单元 330 开始工作,根据输入的运算序号、读使能信号以及最大支持滤波系数个数和实际滤波系数个数信号,产生有效偏移地址,从而读出正确位置的待滤波数据。

[0121] 本实施例中,由于每产生 BS = 4 个待滤波数据需要读取 K = 6 次缓存,故运算序号为一串 $\{0,1,2,3,4,5\}$ 的循环码。当产生第一组 BS = 4 个滤波结果数据时,有效偏移地址= $\{1,2,3,4,5,6\}$ 。该有效偏移地址产生如图 6 所示。故此时前 6 次读取待滤波数据缓存器返回的待滤波数据分别为 $\{0,0,0,0\}$ , $\{0,0,0,0\}$ , $\{0,0,0,1\}$ , $\{0,0,1,2\}$ , $\{0,1,2,3\}$ , $\{1,2,3,4\}$ 。

[0122] 当图 2 中的乘法器运算 K = 6 次后,即可得出前 BS = 4 个结果值,之后需要更新缓存器实体 310 的值,即从存储器里面取值。此时图 2 中 FIR 滤波器中输出给待滤波数据缓存器 30 的移位信号有效,缓存器会有一个整体的移位,移位的幅度为 BS = 4。移位后缓存器待滤波数据如图 11B 所示。

[0123] 此时已经得出了 BS 个滤波输出数据,并且缓存器已经做好相应待滤波数据的更新,配合运算部件进行下面 BS 个结果待滤波数据的运算,期间读缓存器和更新缓存机制不变。

[0124] 当 K' = 3BS + 2 时,其实施例如下:此时缓冲器大小至少为 5BS + 1。同时依然假定运算单元尺寸,即 BS = 4,实际滤波系数个数为 K = 6,此时 K' = 14,缓冲区大小至少为 21。 [0125] 在使用的开始阶段,本实施例需要先进行初始化,此时初始化逻辑单元 201 工作,将数缓存器地址  $0 \sim 12$  的部分初始化为 0,将地址  $13 \sim 20$  的部分初始化为特定的值,该值从存储器取得,每次从存储器可以取 BS = 4 个待滤波数据,共需要取 2 次。缓存器编址及初始化后的情况如图 12A 所示。

[0126] 初始化完毕后,运算部件即采用图 2 所示中的乘法器需要读取该缓存器,此时读逻辑单元 330 开始工作,根据输入的运算序号、读使能信号以及最大支持滤波系数个数和实际滤波系数个数信号,产生有效偏移地址,从而读出正确位置的待滤波数据。

[0127] 本实施例中,由于每产生 BS = 4 个待滤波数据需要读取 K = 6 次缓存,故运算序号为一串  $\{0,1,2,3,4,5\}$  的循环码。当产生第一组 BS = 4 个滤波结果数据时,有效偏移地址=  $\{8,9,10,11,12,13\}$ 。该有效偏移地址产生如图 6 所示。故此时前 6 次读取待滤波数据缓存器返回的待滤波数据分别为  $\{0,0,0,0\}$ ,  $\{0,0,0,0\}$ ,  $\{0,0,0,1\}$ ,  $\{0,0,1,2\}$ ,  $\{0,1,2,3\}$ ,  $\{1,2,3,4\}$ 。

[0128] 当图 2 中的乘法器运算 K = 6 次后,即可得出前 BS = 4 个结果值,之后需要更新缓存器实体 310 的值,即从存储器里面取值。此时图 2 中 FIR 滤波器中输出给待滤波数据缓存器 30 的移位信号有效,缓存器会有一个整体的移位,移位的幅度为 BS = 4。移位后缓存器待滤波数据如图 12B 所示。

[0129] 此时已经得出了 BS 个滤波输出数据,并且缓存器已经做好相应待滤波数据的更新,配合运算部件进行下面 BS 个结果待滤波数据的运算,期间读缓存器和更新缓存机制不变。

[0130] 特别说明的是,如果待滤波数据个数  $N_x$  不能被 BS 整除,整个运算过程保持不变,但是在最后一次运算得出的 BS 个结果中,只有  $N_m$  个有效滤波结果数据,  $N_m$  为  $N_x$  除以 BS 所

得的余数。最后一次将数据写回存储器时,只将该 N. 个有效结果写回。

[0131] 上述滤波器的实现可以应用在 FPGA 的滤波器设计中,也可以将该滤波器行为定义成一条处理器指令,在 ASIC 内部实现。

[0132] 从上述实施例可知,本发明 FIR 滤波器具有以下有益效果:

[0133] 1)并行计算的高效率,本发明采用BS个并行的乘法单元,可以同时进行BS个乘法运算,同时将BS个乘法结果同相应的寄存器中值并行进行BS个加法运算,从而大大提高了运算效率,节约运算时间,并且所有的控制信号均是数字信号,避免了采用延迟单元等模拟单元所带来的运算不准确性,提高了运算精度;

[0134] 2) 可重构性,本发明基于乘累加器的 FIR 滤波器,在 2BS 个滤波系数范围内,均取得高效的滤波效果,即使当滤波系数的个数发生变化时,只要其在缓存空间的范围之内,就不用重新更改相应硬件,从而实现了相当好的重构性;

[0135] 3) 待滤波数据高利用率,本发明通过在整个算法层面分析,使用待滤波数据缓存器 30 和系数缓存器 20 结构,充分利用了待滤波数据局部性原理,没有重复加载待滤波数据的现象,并且每访问一次存储器,可得出 BS 个结果,减少存储器访问次数,从而达到了"一次读取,多次计算"的效果,进而降低了整个设计的功耗。

[0136] 以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

图 1

图 2

图 3

图 4

图 5a

图 5b

图 6

图 7a

图 7b

| 1  | 2  | <br>16 |

|----|----|--------|

| 17 | 18 | <br>32 |

| 33 | 34 | <br>48 |

| 49 | 50 | <br>64 |

| 65 | 66 | <br>80 |

图 8a

16

32

48

64

80

图 8b

地址 32

图 10a

图 10b

图 10c

图 11A

图 11B

图 12A

图 12B